The Taiwan Semiconductor Risk: The $10 Trillion Chokepoint

Part 4 of The Hidden AI Winners Series — The Single Largest Unpriced Shock in Global Markets

Series Context

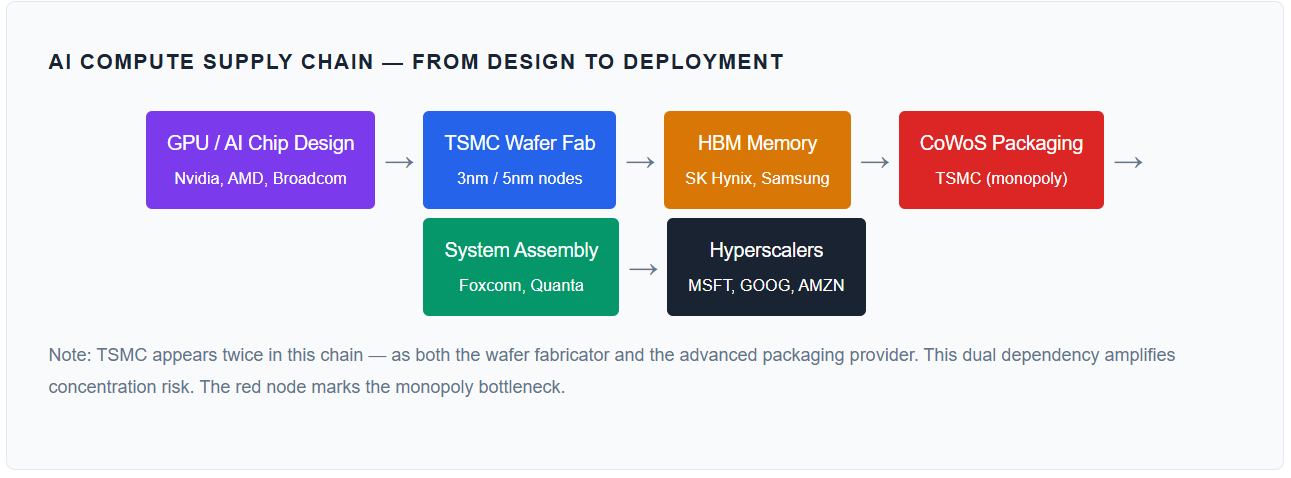

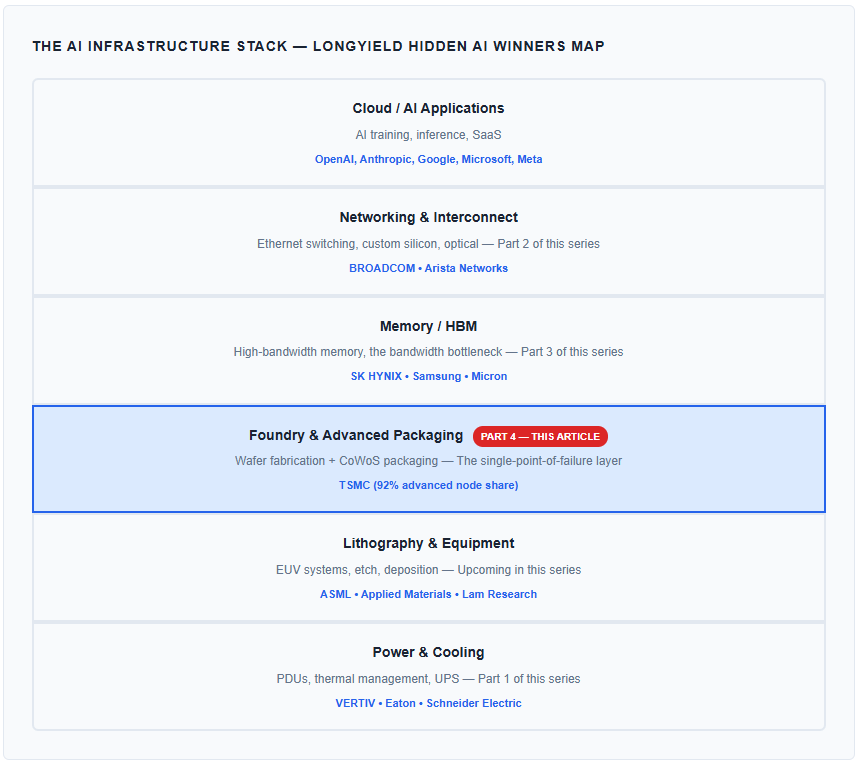

In Parts 1–3 of The Hidden AI Winners series, we mapped the critical infrastructure layers enabling the AI economy: power and cooling (Vertiv), networking and custom silicon (Broadcom), and high-bandwidth memory (SK Hynix). Each analysis identified a structural bottleneck where a small number of companies capture outsized economic value from the AI buildout.

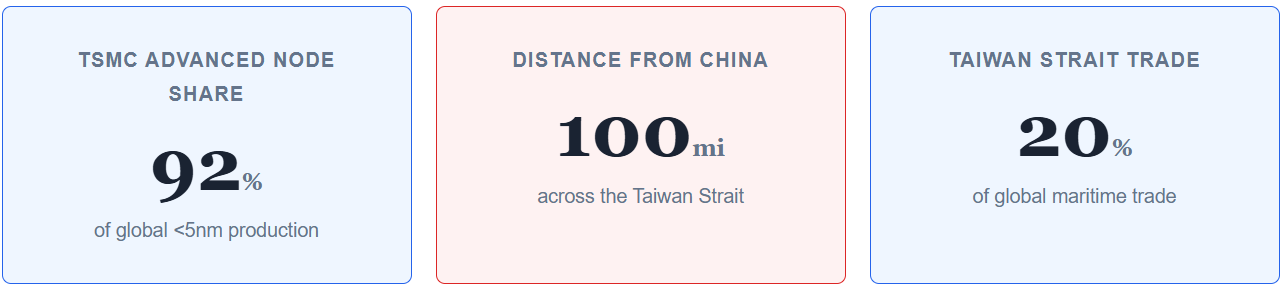

Part 4 steps back from individual company analysis to address the risk that renders every previous thesis conditional: what happens if the foundry layer disappears? TSMC — the single company that manufactures the chips analyzed in every prior installment — operates almost entirely from one island 100 miles from mainland China. This article models the financial and economic consequences of a Taiwan disruption scenario, quantifies the concentration risk, and provides a probability-weighted framework for how markets may reprice.

This is not a generic geopolitics essay. It is an investor-grade shock model with explicit assumptions, clear math, and a framework for scenario-based positioning.

Executive Summary

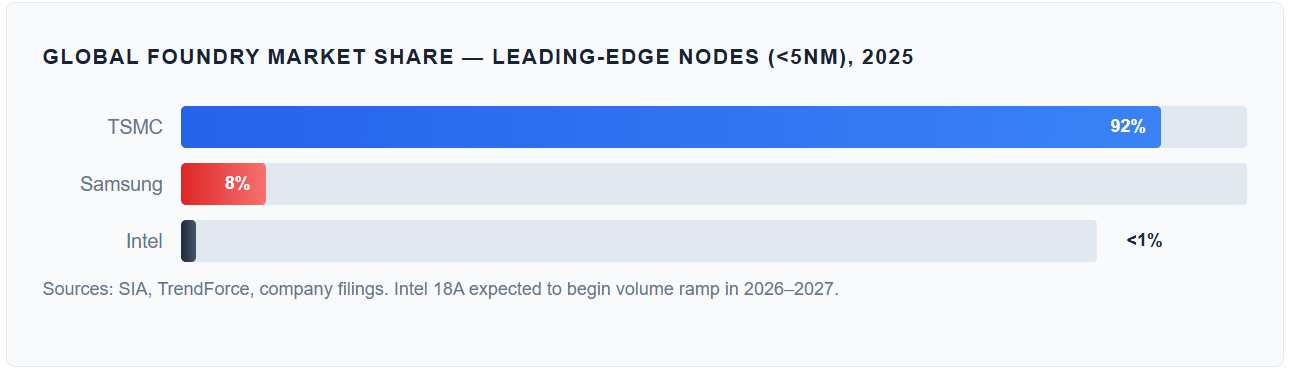

Taiwan Semiconductor Manufacturing Company (TSMC) controls approximately 70% of global foundry revenue and over 90% of the world’s most advanced chip production at leading-edge nodes (3nm and 5nm). This concentration represents arguably the single largest unpriced supply-chain risk in global markets. A disruption to TSMC’s operations — whether from a military conflict, blockade, or natural disaster — would propagate through every major sector of the global economy within days.

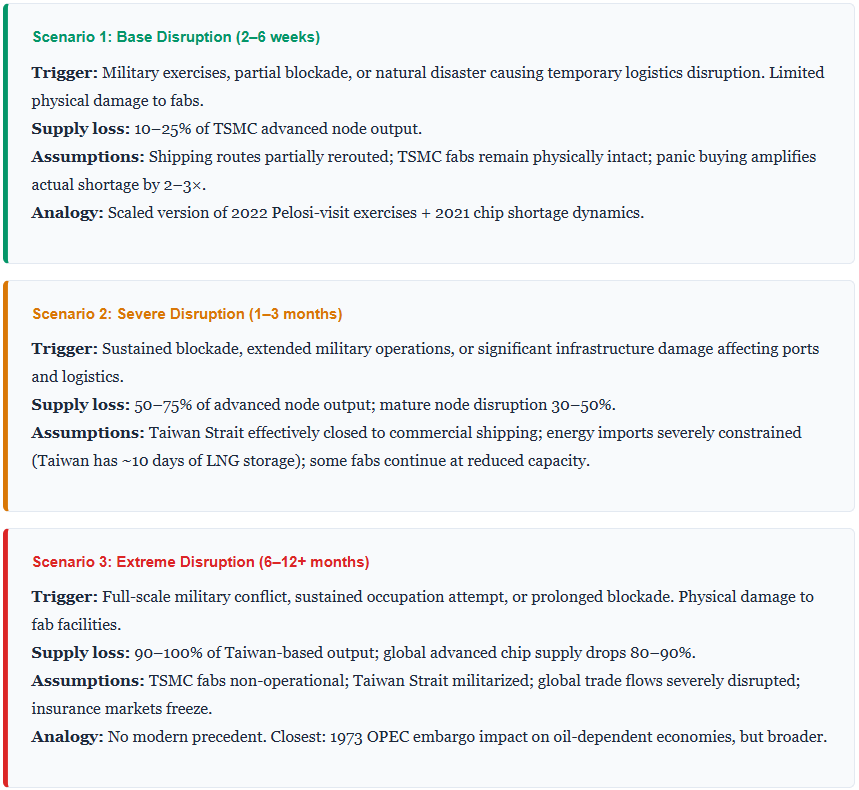

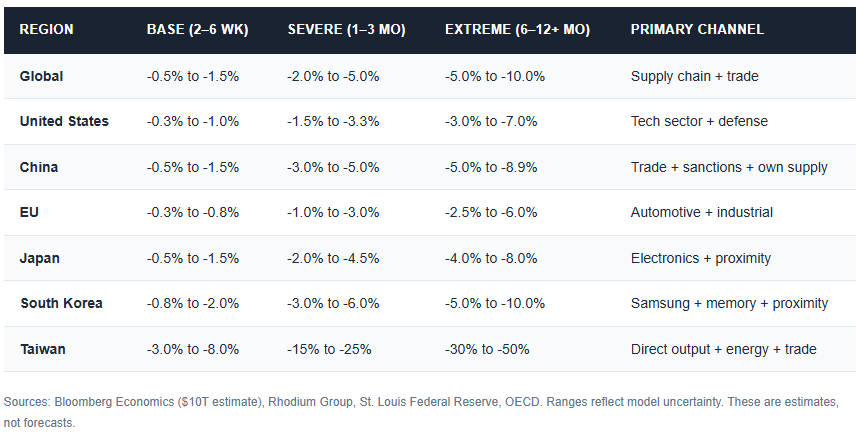

We model three disruption scenarios — Base (2–6 weeks), Severe (1–3 months), and Extreme (6–12+ months) — and estimate global GDP impacts ranging from 0.5–1.5% in the mildest case to 5–10% in a sustained disruption. Bloomberg Economics estimates a full Taiwan conflict at approximately $10 trillion in first-year costs. There is no near-term substitute: TSMC Arizona’s first advanced node fab is not expected to reach 2nm volume production until 2030, and Samsung and Intel remain years behind at cutting-edge nodes.

Meanwhile, China’s military capabilities continue to advance toward a 2027 readiness threshold. U.S. deterrence bandwidth is stretched across multiple theaters. We assess this risk as systematically underpriced across global equity, rates, FX, and commodity markets. This report provides an investor-grade framework for understanding, monitoring, and positioning around the Taiwan chokepoint.

Key Takeaways

Monopoly concentration: TSMC produces ~92% of the world’s most advanced semiconductors (<5nm). No other company can substitute this capacity within 3–5 years.

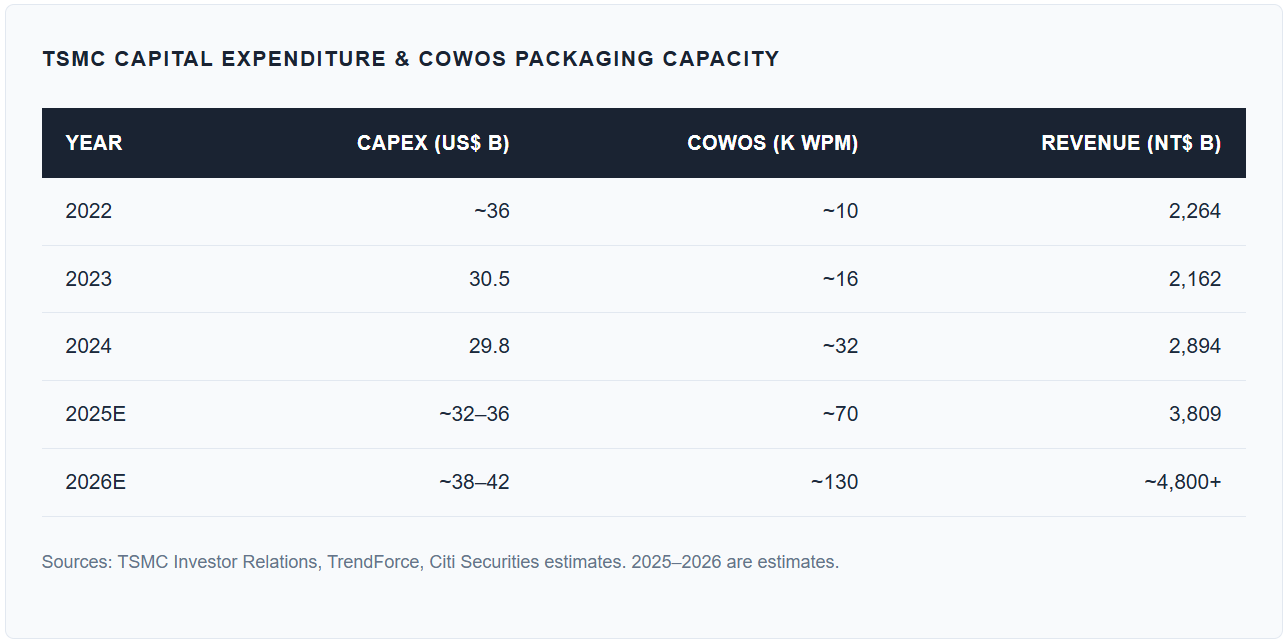

Revenue scale: The global semiconductor market reached $792B in 2025 (SIA). TSMC alone generated ~$120B in revenue, growing 36% year-over-year.

AI bottleneck: TSMC’s CoWoS advanced packaging — critical for every major AI accelerator — is fully booked through 2026 with demand growing 113% annually.

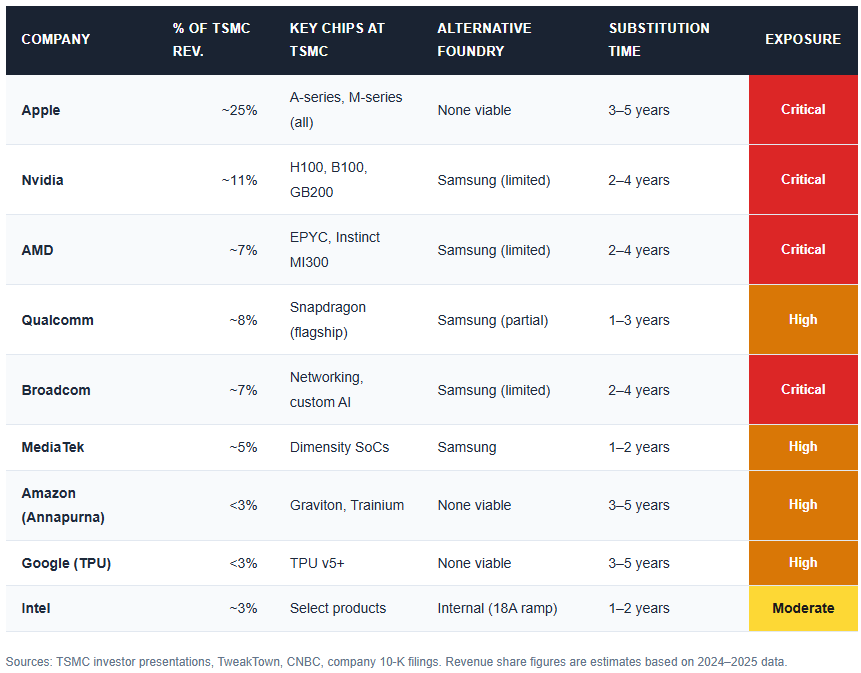

Customer lock-in: Apple (25% of TSMC revenue), Nvidia (11%), AMD (7%), Qualcomm (8%), and Broadcom (7%) have no viable alternative foundry for their most advanced chips.

GDP at risk: Bloomberg Economics estimates a Taiwan conflict at ~$10 trillion globally (~10% of world GDP), exceeding the economic damage from COVID-19.

Shipping chokepoint: ~20% of global maritime trade ($2.45T) and 44% of the world’s container fleet transit the Taiwan Strait annually.

No fast substitution: Building a new leading-edge fab takes 3–4 years and costs $10B+. TSMC Arizona’s 2nm volume production is targeted for 2030.

Military timeline: China’s PLA is targeting 2027 for Taiwan-scenario readiness. December 2025’s exercises were described as the largest Taiwan-focused drills ever conducted.

Deterrence strain: U.S. military commitments in Ukraine and the Middle East compete for the same weapons systems, logistics bandwidth, and political capital needed for Taiwan deterrence.

Silicon shield eroding: Overseas fab expansion and U.S. export controls are gradually diluting Taiwan’s semiconductor leverage as a deterrent.

Market mispricing: Prediction markets imply ~22% conflict probability by 2027, yet implied volatility and geopolitical risk premia remain historically subdued relative to this tail risk.

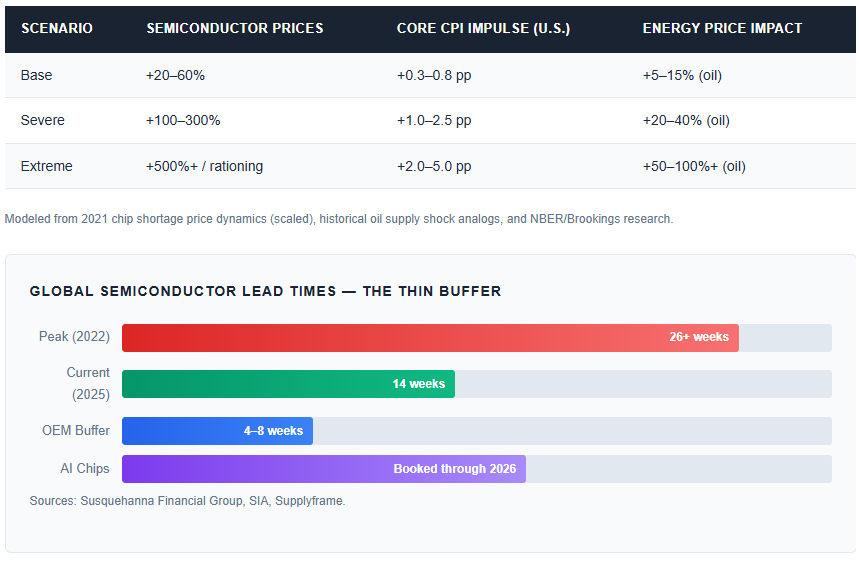

Inventory buffer is thin: Global semiconductor lead times have normalized to ~14 weeks, but most end-users hold only 4–8 weeks of chip inventory.

The Chokepoint: Why Taiwan Matters

The global semiconductor supply chain has a structural single point of failure, and it sits on an island 100 miles from mainland China. Taiwan — specifically TSMC — controls the production of virtually all leading-edge logic chips that power smartphones, data centers, AI training infrastructure, advanced weapons systems, and autonomous vehicles.

Node Architecture: Leading-Edge vs. Mature

Semiconductor manufacturing is segmented by “node” — the feature size of transistors measured in nanometers. Leading-edge nodes (currently 3nm and 5nm) require the most advanced equipment, process engineering, and capital investment. These chips power the highest-performance applications: Apple’s A-series and M-series processors, Nvidia’s H100/B100 AI accelerators, AMD’s data center GPUs, and Qualcomm’s flagship mobile SoCs. Mature nodes (28nm and above) serve automotive, industrial, and consumer IoT markets more broadly. While mature nodes are produced by multiple foundries including Chinese fabs, leading-edge production is functionally a Taiwan monopoly.

TSMC’s Role in Advanced Packaging

Beyond wafer fabrication, TSMC dominates advanced packaging — the process of integrating multiple chiplets, high-bandwidth memory (HBM), and logic dies into a single package. TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) technology is the enabling platform for every major AI accelerator chip. CoWoS capacity reached ~32K wafers/month at end-2024, is projected at ~70K by end-2025, and ~130K by end-2026. Demand is growing at 113% annually, and capacity is fully booked through 2026. Advanced packaging has become the binding constraint on global AI compute scaling — not wafer fabrication itself.

Dependency Map: Who Depends on TSMC

TSMC’s customer list reads as a roster of the world’s most valuable technology companies. Most are “fabless” — they design chips but own no manufacturing capacity. Their entire product roadmap depends on TSMC allocation.

The concentration is starkest in AI infrastructure. Every major AI accelerator chip — Nvidia’s H100/B100, AMD’s MI300X, Google’s TPU, Amazon’s Trainium, Broadcom’s custom ASICs — is manufactured and packaged exclusively by TSMC. There is no second source. A TSMC disruption is, functionally, an AI compute disruption.

Shock Model: What Breaks First

We model disruption impact across four time horizons. The cascading nature of semiconductor supply chains means that relatively short disruptions produce disproportionately large downstream effects.

Scenario Framework

Macro Impact Modeling

Inflation Impulse

The inflationary transmission operates through two channels: direct semiconductor price spikes propagating into finished goods, and energy price shocks from shipping route disruption. During the 2021 chip shortage — approximately 10–15% of the supply loss in our Severe scenario — core inflation impact was estimated at 0.1–0.4 percentage points (Brookings). Supply chain disruptions during COVID accounted for ~40% of the increase in manufacturers’ unit cost expectations (NBER).